[Newton, Massachusetts, June 26, 2024] – FortifyIQ, a leading provider of advanced security semiconductor solutions, announces the release of FortiPKA-RISC-V, a revolutionary public key accelerator, with enhanced performance and area, designed to meet the demanding requirements of modern asymmetric cryptography algorithms. The PKA streamlines complex processes such as encryption/decryption, and digital signing/signature verification.

FortiPKA-RISC-V’s Key Features at a Glance:

- Streamlines encryption/decryption and digital signing/verification.

- Unique algorithms remove the need for Montgomery domain transformations.

- Configurable countermeasures against side-channel and fault injection attacks.

- Seamless integration into customer products, with extensive customization options.

- Supports large integer modular arithmetic up to 4096 bits for RSA and ECC.

Key Features:

- Extensive customization options on software, firmware, and hardware levels, supported by comprehensive deliverables and documentation.

- Implementation of cryptographic algorithms in firmware executed on an internal miniature RISC-V core, with an extended instruction set including FortifyIQ’s modular arithmetic instructions.

- Hardware configuration options enable customization for specific applications, balancing area and performance.

- Support for CPU interfacing through AMBA AXI4, APB, AHB, or custom memory-like slave interface.

- Comprehensive software library facilitating high-level operations including encryption, decryption, signing, and verifying for a variety of cryptographic algorithms.

- Modular exponentiation operations with up to 4096-bit modulus.

- Prime field ECC operations with up to 571-bit modulus.

- Unique algorithms eliminate the necessity to transform data to and from the Montgomery domain, resulting in superior performance, area and execution.

- Incorporates robust countermeasures against modern side-channel and fault injection attacks, with configurable protection levels to enhance security according to specific requirements.

- Technology-agnostic: seamless integration into customer products.

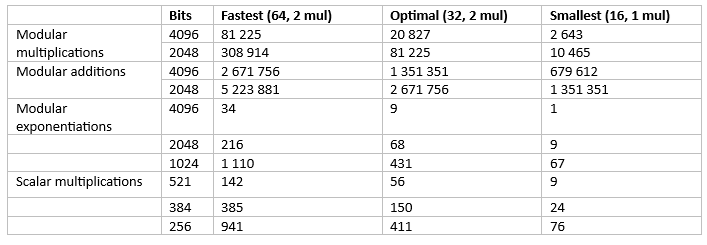

Performance and Area Metrics:

(The performance/area metrics can vary depending on the specific configuration, interface, and chosen standard cell library.)

- Fastest implementation: 58 kGE and 68 Op/s for 2048-bit RSA, 431 Op/s for 1024-bit RSA, 150 Op/s for 384-bit scalar multiplication

- Smallest implementation: 33 kGE and 67 Op/s for 1024-bit RSA, 24 Op/s for 384-bit scalar multiplication

- Operates at up to 350 MHz on the 45 nm process.

For more information about FortiPKA-RISC-V and its capabilities, please visit FortifyIQ.com or contact dvorah@fortifyiq.com

Other Products:

In addition to FortiPKA-RISC-V, FortifyIQ’s product range includes Ultra Low Power AES IP cores resilient to SCA and FIA. These cores are suitable for use in IoT devices, automotive systems, healthcare applications, etc., providing strong security features while consuming minimal power, offering a low gate count and maintaining equivalent performance and latency compared to conventional unprotected cores. Their lightweight SCA and FIA protected HMAC SHA2 also maintains the naive implementations’ performance and latency.

FortifyIQ’s high-performance SW libraries protect already deployed field devices from SCA and FIA by a simple software download. They are based on the same security proven algorithm as FortifyIQ’s ultra-low power IP cores, and are silicon proven. They have extremely high performance, such that even on a low-end processor the performance is high enough for Ultra HD video streaming.

Contact: Dvorah Belenky

Partnership Initiatives

dvorah@fortifyiq.com

![]()