This is a story of one guy who wanted to work on a 3 months summer project and ended up changing the semiconductor processor market forever.

RISC-V, pronounced as Risk-Five, is an open specification of an ISA, or Instruction Set Architecture. It’s an open source, transparent and royalty free computer processor architecture. The RISC-V project came from UC Berkeley to solve some of the existing issues with current processor architecture.

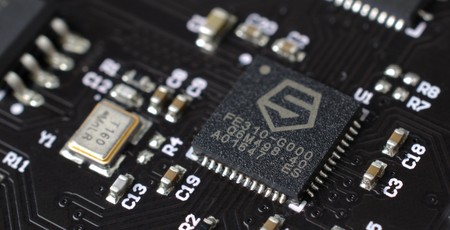

![]()

The idea behind open source is to enable companies to freely adapt, extend and implement to any size or performance processor. This means a huge win for both the consumer and vendors. Nvidia, Western Digital and many other vendors are about to ship (or shipping already) CPUs based on RISC-V architecture.

RISC-V has an array of 32 registers holding the processor’s running state, and the data being immediately operated on. This array is enabling the CPU to run without (or with minimum) external memory activities for many of the basic operation – this allows lower power consumption and increased performance. RISC-V has 32-bit, 64-bit and 128-bit variants.

The RISC-V website offers wealth of information, design tools, boot builders, programming languages and operating systems. In addition to that, there are a few of IC simulations, and designs that can be download into various FPGAs.

RISC-V Foundation

The RISC-V Foundation was founded in 2015, a non-profit corporation that directs the future development and the adoption of the RISC-V ISA. Currently, there are 325 members and all members have access to and participate in the development of the RISC-V ISA specifications and related HW / SW ecosystem. The Foundation has a Board of Directors comprising seven representatives from Bluespec, Inc.; Google; Microsemi; NVIDIA; NXP; University of California, Berkeley; and Western Digital.

RISC-V Benefits